- 您现在的位置:买卖IC网 > Sheet目录3876 > PIC18F14K50-I/SS (Microchip Technology)IC PIC MCU FLASH 8KX16 20-SSOP

PIC18F/LF1XK50

DS41350E-page 116

Preliminary

2010 Microchip Technology Inc.

13.5

Resetting Timer3 Using the CCP

Special Event Trigger

If CCP1 module is configured to use Timer3 and to gen-

erate a Special Event Trigger in Compare mode

(CCP1M<3:0>), this signal will reset Timer3. It will also

start an A/D conversion if the A/D module is enabled

(see Section 17.2.8 “Special Event Trigger” for more

information).

The module must be configured as either a timer or

synchronous counter to take advantage of this feature.

When used this way, the CCPR1H:CCPR1L register

pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode,

the Reset operation may not work.

In the event that a write to Timer3 coincides with a

Special Event Trigger from a CCP module, the write will

take precedence.

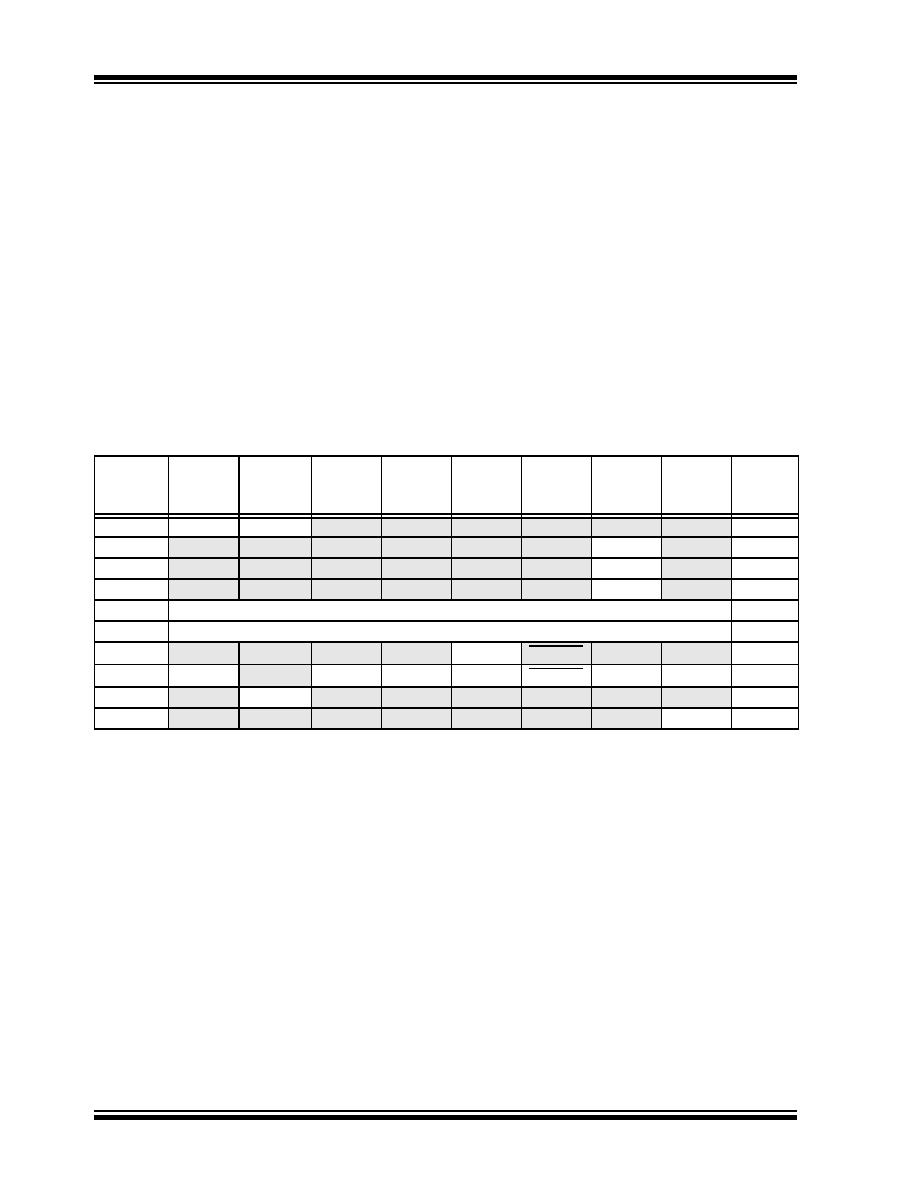

TABLE 13-1:

REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reset

Values

on page

INTCON

GIE/GIEH PEIE/GIEL

TMR0IE

INT0IE

RABIE

TMR0IF

INT0IF

RABIF

PIR2

OSCFIF

C1IF

C2IF

EEIF

BCLIF

USBIF

TMR3IF

CCP2IF

PIE2

OSCFIE

C1IE

C2IE

EEIE

BCLIE

USBIE

TMR3IE

CCP2IE

IPR2

OSCFIP

C1IP

C2IP

EEIP

BCLIP

USBIP

TMR3IP

CCP2IP

TMR3L

Timer3 Register, Low Byte

TMR3H

Timer3 Register, High Byte

T1CON

RD16

T1RUN

T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

TMR1CS

TMR1ON

T3CON

RD16

—

T3CKPS1 T3CKPS0

T3CCP1

T3SYNC

TMR3CS

TMR3ON

TRISC

TRISC7

TRISC6

TRISC5

TRISC4

TRISC3

TRISC2

TRISC1

TRISC0

ANSELH

—

ANS11

ANS10

ANS9

ANS8

Legend: — = unimplemented, read as ‘0’. Shaded cells are not used by the Timer3 module.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F08KL302-I/ML

IC MCU 16BIT 8KB FLASH 28-QFN

PIC24F08KL302-I/MQ

IC MCU 16BIT 8KB FLASH 28-QFN

PIC16LF627A-I/P

IC MCU FLASH 1KX14 EEPROM 18DIP

PIC18F25K20-I/SO

IC PIC MCU FLASH 16KX16 28SOIC

PIC24F08KL301-I/SO

IC MCU 16BIT 8KB FLASH 20-SOIC

PIC24F04KL101-I/P

IC MCU 16BIT 4KB FLASH 20-PDIP

PIC16LC56A-04/SO

IC MCU OTP 1KX12 18SOIC

PIC16LF74-I/PTG

IC MCU FLASH 4KX14 44TQFP

相关代理商/技术参数

PIC18F14K50T-I/SO

功能描述:8位微控制器 -MCU 16KB Flash 768 RAM15 I/O 10-B ADC USB 2.0

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F14K50T-I/SS

功能描述:8位微控制器 -MCU 16KB Flash 768 RAM15 I/O 10-B ADC USB 2.0

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-E/SO

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-E/SP

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-I/SO

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-I/SO

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F2220 SOIC28

PIC18F2220-I/SOC03

制造商:Microchip Technology Inc 功能描述:

PIC18F2220-I/SP

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT